## 微小遅延故障検出用テスト容易化設計の開発

[キーワード:テスト容易化設計,遅延故障,テストコスト削減] 准教授 四柳 浩之

## 内容:

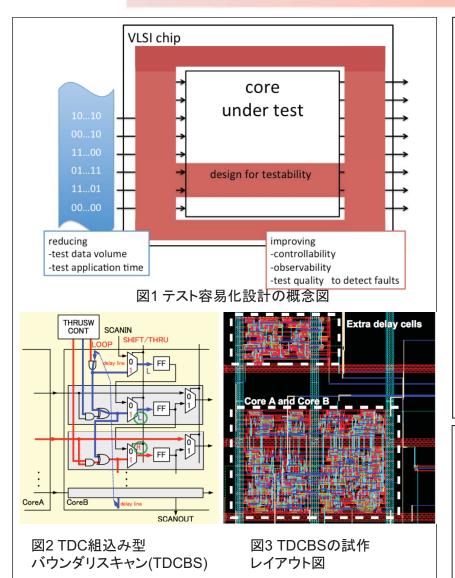

LSIの高集積化に伴い、テストコストが重要な問題となって いる. テストコストの低減のために. 様々なテスト容易化設計 が提案・使用されている。テスト容易化設計は、図1の概念 図のように検査対象回路(コア)の内部および外部にテストコ ストを低減させるための付加回路を設ける技術である. 我々 は、特に近年問題となっている微小遅延故障を対象に、テス トデータ量、テスト実行時間、テスト用の付加面積の低減や、 テスト品質の向上を目的とした研究を行っている。図2に開 発したテスト容易化設計の1例を示す、VLSIチップ内部およ びVLSIチップ間接続で発生する微小遅延の検出を容易とす るために、Time-to-Digital Converter (TDC) を構成可能なバ ウンダリスキャン回路(TDCBS)を作成し、信号遷移の発生し たタイミングの測定を可能とした。これにより、クロック周期内 に信号遷移が収まっているか否かのテストのみではなく、見 逃しの少ない遅延故障テストを行うことができる. 提案したテ スト容易化設計の故障検出能力などの有効性に関しては. シミュレーションおよび試作チップによる評価を行っている.

分野: 計算機システム

専門: 計算機工学

E-mail: yanagi4@ee.tokushima-u.ac.jp

Tel. 088-656-9183

Fax: 088-656-9183